**Application Note**

March 17, 2009

AN1458.0

### ISL7457SRH TID Rating

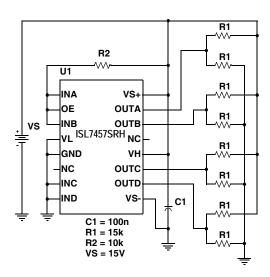

The ISL7457SRH is specified for 10krads(Si) minimum TID in SMD 5962-08230 when continuously biased as shown in Figure 1.

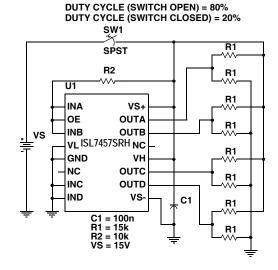

In many cases a 10krad(Si) TID rating is not adequate to meet mission requirements, so a method to extend the TID capability is desired. Figure 2 shows a radiation exposure circuit that biases the ISL7457SRH only 20% of the time. For the other 80% of the time, the ISL7457SRH is unbiased. Devices irradiated in this manner have demonstrated acceptable post-rad parametric limits after 50krad(Si) TID, as indicated in the Electrical Specification tables of this application note. Please note, however, that the post-50krad electrical specifications shown herein are not specified in or guaranteed by SMD 5962-08230.

### **Imaging Applications**

Some camera CCD driver applications do not require 100% availability. In these situations, the ISL7457SRH can be left unbiased until there is a need to image. When imaging is required, the ISL7457SRH can be quickly biased by simply closing a switch. As long as the duty-cycle of the application does not exceed 20%, the TID capability can be extended up to 50krad(Si).

#### **Conclusions**

A simple method to extend the TID capability of the ISL7457SRH to 50krad(Si) has been described. This method can be applied to any space-based system that uses the device as long as 20% availability is acceptable.

FIGURE 1. RAD EXPOSURE CIRCUIT (BIAS DUTY CYCLE = 100%)

FIGURE 2. RAD EXPOSURE CIRCUIT (BIAS DUTY CYCLE = 20%)

# **Application Note 1458**

$\begin{tabular}{ll} \textbf{Electrical Specifications} & V_S+=V_H=5V\ \pm 10\%,\ V_{S^-}=V_L=0V,\ OE=V_S+,\ T_A=\pm 25^\circ C,\ Post\ 50krad(Si)\ unless\ otherwise\ specified.\ Refer to\ Figure\ 2\ for\ radiation\ exposure\ circuit\ biasing. \end{tabular}$

| PARAMETER            | DESCRIPTION                                 | CONDITION                                                      | MIN  | TYP | MAX | UNIT |

|----------------------|---------------------------------------------|----------------------------------------------------------------|------|-----|-----|------|

| INPUT                | <u>'</u>                                    |                                                                | Į.   | U.  | U.  | 1    |

| V <sub>IH</sub>      | Logic "1" Input Voltage                     |                                                                | 2    |     |     | V    |

| I <sub>IH</sub>      | Logic "1" Input Current                     | $INx = V_S +$                                                  | -10  |     | 10  | μA   |

| V <sub>IL</sub>      | Logic "0" Input Voltage                     |                                                                |      |     | 0.6 | V    |

| I <sub>IL</sub>      | Logic "0" Input Current                     | INx = 0V                                                       | -10  |     | 10  | μA   |

| OUTPUT               |                                             |                                                                | 1    | •   |     |      |

| R <sub>OH</sub>      | ON Resistance V <sub>H</sub> to OUTx        | INx = V <sub>S</sub> +, I <sub>OUTx</sub> = -100mA             |      |     | 12  | Ω    |

| R <sub>OL</sub>      | ON Resistance V <sub>L</sub> to OUTx        | INx = 0V, I <sub>OUTx</sub> = +100mA                           |      |     | 7   | Ω    |

| I <sub>LEAK+</sub>   | Positive Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S+$                       |      |     | 300 | μΑ   |

| I <sub>LEAK</sub> -  | Negative Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S-$                       | -50  |     |     | μΑ   |

| POWER SUPPL          | .Y                                          | ,                                                              |      |     |     |      |

| I <sub>S+</sub>      | V <sub>S</sub> + Supply Current             | INx = 0V and V <sub>S</sub> +                                  |      |     | 5   | mA   |

| I <sub>S</sub> -     | V <sub>S</sub> - Supply Current             | INx = 0V and V <sub>S</sub> +                                  | -5   |     |     | mA   |

| I <sub>H</sub>       | V <sub>H</sub> Supply Current               | INx = 0V and V <sub>S</sub> +                                  |      |     | 650 | μΑ   |

| IL                   | V <sub>L</sub> Supply Current               | INx = 0V and V <sub>S</sub> +                                  | -650 |     |     | μΑ   |

| SWITCHING CH         | HARACTERISTICS                              | ,                                                              | J.   |     |     |      |

| t <sub>R</sub>       | Rise Time                                   | INx = 0V to 4.5V step, C <sub>L</sub> = 1nF                    |      |     | 40  | ns   |

| t <sub>F</sub>       | Fall Time                                   | $INx = 4.5V \text{ to } 0V \text{ step, } C_L = 1nF$           |      |     | 26  | ns   |

| $t_{RF\Delta}$       | t <sub>R</sub> , t <sub>F</sub> Mismatch    | C <sub>L</sub> = 1nF                                           |      |     | 5   | ns   |

| t <sub>D</sub> +     | Turn-On Delay Time                          | INx = 0V to 4.5V step, C <sub>L</sub> = 1nF                    |      |     | 30  | ns   |

| t <sub>D</sub> -     | Turn-Off Delay Time                         | $INx = 4.5V \text{ to } 0V \text{ step, } C_L = 1nF$           |      |     | 40  | ns   |

| t <sub>DD</sub>      | t <sub>D</sub> +, t <sub>D</sub> - Mismatch | C <sub>L</sub> = 1nF                                           |      |     | 12  | ns   |

| t <sub>ENABLE</sub>  | Enable Delay Time                           | INx = V <sub>S</sub> +, OE = 0V to 4.5V step, $R_L = 1k\Omega$ |      |     | 35  | ns   |

| <sup>t</sup> DISABLE | Disable Delay Time                          | INX = $V_S$ +, OE = 4.5V to 0V step, $R_L$ = 1k $\Omega$       |      |     | 50  | ns   |

## **Application Note 1458**

### **Electrical Specifications**

$V_S$ + =  $V_H$  = 15V ±10%,  $V_S$ - =  $V_L$ = 0V, OE =  $V_S$ +,  $T_A$  = +25°C, Post 50krad(Si) unless otherwise specified. Refer to Figure 2 for radiation exposure circuit biasing.

| PARAMETER            | DESCRIPTION                                 | CONDITION                                              | MIN  | TYP | MAX | UNIT |

|----------------------|---------------------------------------------|--------------------------------------------------------|------|-----|-----|------|

| INPUT                |                                             | ·                                                      |      |     |     |      |

| V <sub>IH</sub>      | Logic "1" Input Voltage                     |                                                        | 2    |     |     | V    |

| I <sub>IH</sub>      | Logic "1" Input Current                     | $INx = V_S +$                                          | -10  |     | 10  | μΑ   |

| V <sub>IL</sub>      | Logic "0" Input Voltage                     |                                                        |      |     | 0.6 | V    |

| I <sub>IL</sub>      | Logic "0" Input Current                     | INx = 0V                                               | -10  |     | 10  | μA   |

| OUTPUT               |                                             |                                                        |      |     |     |      |

| R <sub>OH</sub>      | ON Resistance V <sub>H</sub> to OUTx        | $INx = V_S+$ , $I_{OUTx} = -100mA$                     |      |     | 5   | Ω    |

| R <sub>OL</sub>      | ON Resistance V <sub>L</sub> to OUTx        | INx = 0V, I <sub>OUTx</sub> = +100mA                   |      |     | 5   | Ω    |

| I <sub>LEAK+</sub>   | Positive Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S+$               |      |     | 300 | μA   |

| I <sub>LEAK</sub> -  | Negative Output Leakage Current             | $INx = V_S+$ , $OE = 0V$ , $OUTx = V_S-$               | -50  |     |     | μΑ   |

| POWER SUPPL          | Y                                           | ·                                                      |      |     |     | ,    |

| I <sub>S+</sub>      | V <sub>S</sub> + Supply Current             | INx = 0V and V <sub>S</sub> +                          |      |     | 5   | mA   |

| I <sub>S</sub> -     | V <sub>S</sub> - Supply Current             | INx = 0V and V <sub>S</sub> +                          | -5   |     |     | mA   |

| I <sub>H</sub>       | V <sub>H</sub> Supply Current               | INx = 0V and V <sub>S</sub> +                          |      |     | 750 | μA   |

| IL                   | V <sub>L</sub> Supply Current               | INx = 0V and V <sub>S</sub> +                          | -750 |     |     | μA   |

| SWITCHING CH         | IARACTERISTICS                              | •                                                      |      | •   |     |      |

| t <sub>R</sub>       | Rise Time                                   | INx = 0V to 5V step, C <sub>L</sub> = 1nF              |      |     | 20  | ns   |

| t <sub>F</sub>       | Fall Time                                   | INx = 5V to 0V step, C <sub>L</sub> = 1nF              |      |     | 20  | ns   |

| $t_{RF\Delta}$       | t <sub>R</sub> , t <sub>F</sub> Mismatch    | C <sub>L</sub> = 1nF                                   |      |     | 3   | ns   |

| t <sub>D</sub> +     | Turn-On Delay Time                          | INx = 0V to 5V step, C <sub>L</sub> = 1nF              |      |     | 20  | ns   |

| t <sub>D</sub> -     | Turn-Off Delay Time                         | INx = 5V to 0V step, C <sub>L</sub> = 1nF              |      |     | 20  | ns   |

| t <sub>DD</sub>      | t <sub>D</sub> +, t <sub>D</sub> - Mismatch | C <sub>L</sub> = 1nF                                   |      |     | 5   | ns   |

| t <sub>ENABLE</sub>  | Enable Delay Time                           | INx = $V_S$ +, OE = 0V to 5V step, $R_L$ = 1k $\Omega$ |      |     | 25  | ns   |

| t <sub>DISABLE</sub> | Disable Delay Time                          | INx = $V_S$ +, OE = 5V to 0V step, $R_L$ = $1k\Omega$  |      |     | 65  | ns   |

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.